AMD shows off Radeon HD 6800 series and Llano Fusion APU performance [video]

![AMD shows off Radeon HD 6800 series and Llano Fusion APU performance [video] AMD shows off Radeon HD 6800 series and Llano Fusion APU performance [video]](https://static.digit.in/default/artImg75x64_5593.jpg)

AMD’s most recent demonstration of the performance of its Fusion APU chips was of the Llano Accelerated Processing Unit (APU), which is expected to be the second to arrive in 2011, after the Ontario APU in late 2011. No word on pricing yet.

Survey

SurveyThe Llano APU is made on GlobalFoundries’ 32nm high-K metal gate (HKMG) process, is DX11-capable and features a quad-core Athlon II-class processor, not the recently unveiled Bobcat architecture. With no L3 cache, the Llano APU chip has a large L2 cache per core, 1MB to be precise. It will feature a higher than 3GHz clock speed, and DDR3 memory.

The demonstration showed a single Llano APU chip processing three separate CPU and GPU tasks simultaneously on Windows 7, including calculating Pi to 32 million decimal places, Microsoft’s nBody DirectCompute, and decoding HD video from a Blu-ray. You can check out a video of the performance demonstration below:

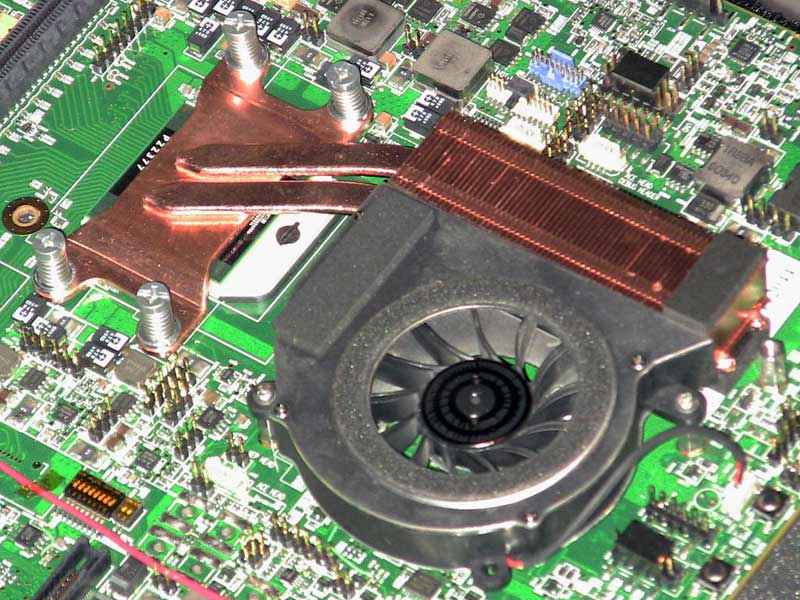

A leaked set of images also show what the chip looks like, seen below:

[RELATED_ARTICLE]An AMD spokesman spoke about the next-gen Fusion processors: “The serial and powerful parallel processing capability of the Llano APU has the potential to make OEMs and consumers re-think their computing experience. The experience potential of Llano is truly incredible, and the demos we showed today on stage provide a glimpse of what this processor is capable of delivering in sleek form factors with long battery life. Everything consumers love about their digital lifestyles today – social networking, gaming, consuming and creating media – can be enhanced with Llano, enabling a more interactive, vivid and immersive experience.”

A spokesman from GlobalFoundries said: “This is an important milestone for Globalfoundires because it is the industry’s first demonstration of a foundry product with HKMG technology. Llano is being manufactured at Fab 1 in Dresden on our next-generation 32nm process technology with gate-first HKMG transistors. We are implementing the gate-first approach to HKMG at the 32/28nm node because it maximizes power efficiency and transistor scaling while minimizing die size and design complexity for our customers. Our 32nm HKMG technology ramp is currently in early production at Fab 1 and we are making continued progress on ramping the process in support of AMD’s 2011 customer commitments.”

AMD also showed off the performance of its upcoming Radeon HD 6800 GPU series, namely the HD 6870 and the HD 6850, with a technical demonstration called Mecha Warrior, which uses the open source physics library, Bullet Physics.